# **CONTENTS**

| 1.  | INTRODUCTION                     | 2  |

|-----|----------------------------------|----|

| 2.  | GENERAL DESCRIPTION              | 3  |

| 2.1 | System Block Diagram             | 3  |

| 2.2 | Front Panel Controls and Display | 3  |

| 2.3 | Rear Panel                       | 7  |

| 3.  | LSC24 OPERATION                  | 11 |

| 3.1 | Record Mode                      | 12 |

| 3.2 | ADDA Mode                        | 13 |

| 3.3 | HQDA Mode                        | 14 |

| 3.4 | Convert Mode                     | 15 |

| 4.  | TECHNICAL DESCRIPTION            | 16 |

| 4.1 | Specification                    | 16 |

| 4.2 | Dimensions                       | 16 |

| 5.  | DECLARATION OF CONFORMITY        | 17 |

| Issue | Date       | Changes                   |

|-------|------------|---------------------------|

| 1.0   | 1/06/2000  | Initial Draft Issue       |

| 1.1   | 13/10/2000 | Corrections & s/w changes |

|       |            |                           |

#### 1. INTRODUCTION

The LSC24 is combined two-channel analogue to digital converter (ADC), digital to analogue converter (DAC) and digital sample rate converter (SRC) intended for use in studio applications.

Section 2.2 of this manual details the function of the front panel controls and indicators whilst Section 3 sumarises the four modes of operation of the LSC24:-

- Convert mode :- Digital to Digital Conversion for sample rate / word length conversion.

- Record mode: Analogue to Digital Conversion with analogue output for the monitoring of the digital output.

- ADDA mode :- Independent Analogue to Digital and Digital to Analogue conversion.

- HQDA mode :- High Quality Digital to Analogue Conversion.

It is recommended that Section 2.2 is read first to obtain a full description of each control and their use.

This manual does not cover the operation of the LSC24 via the remote interface.

# 2. General Description

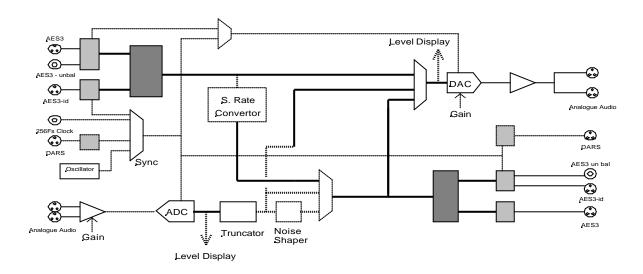

### 2.1 System Block Diagram

The above block diagram illustrates the major function blocks within the LSC24 and the interconnections between these blocks. The dotted lines represent the clocks, the fine lines the analogue signal flow and the thicker lines the digital signal paths.

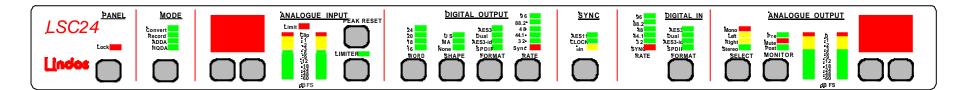

#### 2.2 Front Panel Controls and Display

All user interface is via front panel buttons and the current system operating configuration will be presented to the operator via the front panel LEDs. Dependent upon the mode of operation of the LSC24 some buttons and LEDs will not function. This is to prevent non valid configuration of the unit.

The unit will automatically power up in the same condition as last used. On power up the LSC24 will recall and configure the stored operating parameters and allow the converters to reach the correct operating temperature. During this time the firmware revision number is displayed on the two coding level displays.

The configuration for each of the four modes is also stored in Non Volatile memory (NVR) to simplify the setting up of the LSC24; these are all automatically recalled when changing between modes.

Please refer to Section 3 for the summary of operation for each of the four operating modes.

Each front panel group (ANALOGUE INPUT, SYNC etc.) is given a sub-section and then each control is detailed within the sub-section.

### 2.2.1 PANEL

#### **LOCK**

This toggles the panel LOCK function. When on, indicated by the red LED, all other panel controls are locked preventing accidental operation and changes to the LSC24.

#### 2.2.2 MODE

Scrolls through the operating modes of the unit; CONVERT, RECORD, ADDA and HQDA.

## 2.2.3 ANALOGUE INPUT

### LEVEL UP / DOWN

Sets the coding level of the analogue to digital conversion. Adjustable from +8dBu ≡0dB FS to +26dBu ≡0dB FS in 1dB steps. Either single key presses for 1dB steps or press and hold to quickly ramp through the levels.

#### LIMITER

This toggles the analogue input 'soft' LIMITER. When on, indicated by the green LED, the limiter circuitry will prevent the ADC from clipping when an large input signal is applied. This 'soft' limiter will begin to operate at – 3dB FS and the red LIMIT LED indicates that the limiter is in operation.

#### **PEAK RESET**

The peak input level display is automatically held until the PEAK RESET button is pressed. This will appear as a static LED with the LEDs below changing with the incoming signal.

## 2.2.4 DIGITAL OUTPUT

#### WORD

Selects the required digital output word lengths. 24,20,18 and 16 bit.

#### SHAPE

Selects the noise shaping filter when truncation of the digital audio is selected; 20,18 or 16 bit word length.

The options are :-

NONE - no noise shaping – Triangular p.d.f. dither only

MA - **M**inimally **A**udible shaping

## US - **U**ltra**S**onic shaping

The US shaper is only selectable with the 88.2kHz and 96kHz sample rates.

#### **FORMAT**

Selects the digital audio output format from the LSC24 unit. This applies to the two rear panel 3pin XLR connectors (A & B) and BNC output.

|                | Rear Panel Connector |               |           |  |

|----------------|----------------------|---------------|-----------|--|

| FORMAT         | XLR 'A' XLR 'B' BNC  |               |           |  |

| AES3           | AES3                 | AES3          | No Output |  |

| DUAL           | ½ rate AES3 –        | ½ rate AES3 – | No Output |  |

|                | Right                | Left          |           |  |

| AES3-id        | No Output            | AES3          | AES3-id   |  |

| (Professional) | -                    |               |           |  |

| SPDIF          | No Output            | AES3          | SPDIF     |  |

| (Consumer)     |                      |               |           |  |

#### **RATE**

Selects the required output sample rate for the digital audio outputs. The 32kHz – 96kHz sample rates are derived from the internal crystal oscillator.

If SYNC is selected the adjacent SYNC control (see 2.2.5) is used to selected the source from one of the three external DARS inputs. The digital outputs are then locked to one of these external inputs.

#### 2.2.5 SYNC

An external synchronisation signal can be selected from either the DARS (**D**igital **A**udio **R**eference **S**ignal)/ AES11 input XLR, external CLOCK (256\*FS) input, or the incoming audio data, =IN.

In HQDA mode this SYNC panel is used to select the sync source for the digital to analogue converters (DACs) [DARS/AES11 and =IN only]

#### 2.2.6 DIGITAL IN

#### **FORMAT**

Selects the digital audio input format to the LSC24 unit. This applies to the two rear panel 3pin XLR connectors (A & B) and BNC input.

|         | Rear Panel Connector        |   |         |

|---------|-----------------------------|---|---------|

| FORMAT  | XLR 'A' XLR 'B' BNC         |   |         |

| AES3    | AES3                        | • | -       |

| DUAL    | ½ rate AES3 – ½ rate AES3 – |   | -       |

|         | Right Left                  |   |         |

| AES3-id | AES                         |   | AES3-id |

| SPDIF   | -                           | - | SPDIF   |

RATE - display only, no control.

Shows the incoming sample rate of the selected source as defined by FORMAT. A flashing SYNC LED indicates no valid digital audio is connected or selected.

## 2.2.7 ANALOGUE OUT

#### SELECT

Used to configure the analogue outputs of the LSC24.

STEREO - normal operation RIGHT- right channel only, left muted

LEFT - left channel only, right muted

MONO - left & right combined from both channels

#### MONITOR

Selects the internal source for the input to the Digital to Analogue converter (DAC). This can be either PRE or POST the noise shaper (RECORD mode only). A MUTE function for all modes operating on both channels is also provided using this control.

#### **OUTPUT LEVEL**

Sets the analogue output level of the digital to analogue conversion. Adjustable from  $0dBFS \equiv -9dBu$  to  $0dBFS \equiv +26dBu$  in 1dB steps. Either single key presses for 1dB steps or press and hold to quickly ramp through the levels.

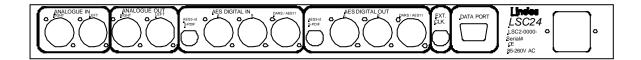

#### 2.3 Rear Panel

The following sub sections detail each rear panel connector of the LSC24.

## 2.3.1 ANALOGUE IN

Two off (left and right channels) 3pin Female XLR connectors providing analogue inputs to the ADC.

$10k\Omega$  input impedance.

Maximum level +26dBu for 0dBFS (with limiter Off).

| Pin | Function       |  |

|-----|----------------|--|

| 1   | Chassis        |  |

| 2   | Audio + (Hot)  |  |

| 3   | Audio – (Cold) |  |

## 2.3.2 ANALOGUE OUT

Two off (left and right channels) analogue output from the DAC. 3pin Male XLR connectors  $50\Omega$  output impedance. Maximum level +26dBu.

| Pin | Function       |  |

|-----|----------------|--|

| 1   | Chassis        |  |

| 2   | Audio + (Hot)  |  |

| 3   | Audio – (Cold) |  |

#### 2.3.3 AES3 DIGITAL IN

## AES3-id (un-balanced AES3) and SPDIF input

Un balanced coaxial BNC connector.

# **AES3 Inputs**

3pin Female XLR connectors, 'A' and 'B'. AES3 digital audio data

| DIGITAL IN FORMAT | XLR 'A'       | XLR 'B'       |

|-------------------|---------------|---------------|

| AES3              | AES3          | 1             |

| DUAL              | ½ rate AES3 – | ½ rate AES3 – |

| (x2 AES3)         | Right         | Left          |

| Pin | Function       |  |

|-----|----------------|--|

| 1   | Chassis        |  |

| 2   | Audio + (Hot)  |  |

| 3   | Audio – (Cold) |  |

# **AES11 / DARS Input**

3pin Female XLR connector. AES11 Synchronisation

| Pin | Function       |  |

|-----|----------------|--|

| 1   | Chassis        |  |

| 2   | Audio + (Hot)  |  |

| 3   | Audio – (Cold) |  |

# 2.3.4 AES Digital OUT

# **AES3-id / SPDIF Output**

Un-balanced BNC coaxial connector.

AES3-id (AES3 un-balanced) – Professional S-PDIF - Consumer

| DIGITAL OUTPUT<br>FORMAT | BNC     |

|--------------------------|---------|

| AES3-id                  | AES3-id |

| SPDIF                    | SPDIF   |

## **AES3 Outputs**

3pin Male XLR connector.

AES3 digital audio data for normal and Dual formats.

|                | ī             |               |

|----------------|---------------|---------------|

| DIGITAL OUTPUT | XLR 'A'       | XLR 'B'       |

| FORMAT         |               |               |

| AES3           | AES3          | AES3          |

| DUAL           | ½ rate AES3 – | ½ rate AES3 – |

| (x2 AES3)      | Right         | Left          |

| AES3-id        | -             | AES3          |

| SPDIF          | -             | AES3          |

| Pin | Function       |  |

|-----|----------------|--|

| 1   | Chassis        |  |

| 2   | Audio + (Hot)  |  |

| 3   | Audio – (Cold) |  |

# **AES11 / DARS Output**

3pin Male XLR connector. AES11

| Pin | Function       |

|-----|----------------|

| 1   | Chassis        |

| 2   | Audio + (Hot)  |

| 3   | Audio – (Cold) |

# 2.3.5 Ext. Clk

BNC connector.

256 x FS External Clock input. Single ended TTL input.

## Example:

A clock frequency of 12.288MHz gives a sample rate of 48kHz

# 2.3.6 Data Port

RS232 / RS422 (internally switched) interface port for external control and monitoring.

9 pin Female 'D' type connector - DCE

| Pin | Function – RS232 | Function – RS422 |

|-----|------------------|------------------|

| 1   |                  |                  |

| 2   | Tx Data (Output) | TxA              |

| 3   | Rx Data (Input)  | RxA              |

| 4   |                  |                  |

| 5   | 0v RS232         |                  |

| 6   |                  | TxB              |

| 7   |                  | RxB              |

| 8   |                  |                  |

| 9   |                  |                  |

# 2.3.7 Mains Input

IEC inlet connector 85 – 264V AC 47-440 Hz or 110 – 370V DC 30W max.

# 3. LSC24 Operation

#### **Record Mode**

In this mode of operation the LSC24 behaves as an ADC with the DAC providing an analogue output for monitoring of either the pre- or post- noise shaper signal.

The Digital Input section is only used if RATE is set to SYNC and SYNC is set to =IN.

#### **ADDA Mode**

In this mode of operation the LSC24 behaves as separate ADC and DAC units. The ADC is synchronised to the internal oscillator, AES11 / DARS input, 256FS clock input or the digital audio input ('=in' mode).

The DAC is synchronised to the digital audio input.

#### **HQDA Mode**

In this mode the analogue input and digital output sections are disabled. The DAC is synchronised to an external input (AES11/DARS or digital audio input) as selected by the SYNC function.

#### **Convert Mode**

In this mode the ADC is disabled and the LSC24 behaves as a SRC with the DAC section used for monitoring.

This conversion is via the SRC unless '=in' SYNC mode is selected

#### 3.1 Record Mode

In this mode of operation the LSC24 behaves as an ADC with the DAC providing an analogue output for monitoring of either the pre- or post- noise shaper signal.

The Digital Input section is only used if RATE is set to SYNC and SYNC is set to =IN or AES11

**Coding Level** Up /Down controls.

Indicates the analogue input signal level for 0dB FS.

#### Peak Reset:

Used to reset last peak level

#### Limiter:

Toggles 'soft' limiter, Green LED indicates on or off.

Limit LED: Indicates when limiter is operating to prevent clipping of the ADC. Starts at -3dB.

#### Word:

Selects required output word length.

#### Shape:

Not valid for 24bit Word. None: no shaping MA: Minimally Audible US: UltraSonic (only valid for 88.2 & 96KHz)

#### Format:

Selects output format and interface connectors.

#### Rate:

Selects required output sample rate or external sync.

# Sync:

Only valid if Rate set to Sync.

> Selects either AES11 **CLOCK** =IN (AES3) clock source.

# **Format**

Incoming

sample rate.

Only valid if

Sync set to

=IN or

Rate

AES11.

Only valid if =IN. Selects input format and interface connectors.

#### Select:

Configures output mode.

#### Monitor:

either pre or post noise shaper. Also used to Mute both channels.

Selects input to DAC.

#### Level

Up /Down controls.

Indicates the analogue output signal level.

#### 3.2 ADDA Mode

In this mode of operation the LSC24 behaves as separate ADC and DAC units. The ADC is synchronised to the internal oscillator, AES11 / DARS input, 256FS clock input or the digital audio input (Sync '=in').

The DAC is synchronised to the digital audio input.

**Coding Level** Up /Down

controls.

Indicates the analogue input signal level for 0dB FS.

## Peak Reset:

Used to reset last peak level

#### Limiter:

Toggles 'soft' limiter. Green LED indicates on or off.

#### Limit LED:

Indicates when limiter is operating to prevent clipping of the ADC. Starts at -3dB.

#### Word:

Selects required output word length.

#### Shape:

Not valid for 24bit Word. None: no shaping MA: Minimally Audible US: UltraSonic (only valid for 88.2 & 96KHz)

#### Format:

Selects output format and interface connectors.

#### Rate:

Selects required output sample rate or external sync.

# Sync: Only valid if

Selects

source.

Incoming Rate set to sample rate. Sync.

## Format: Selects input

Rate:

format and either AES11 interface **CLOCK** connectors. =IN (AES3) clock

# Select:

Configures output mode.

#### Monitor:

Selects either Mute or listen (Post) for both channels.

#### Level

Up /Down controls.

Indicates the analogue output signal level.

#### 3.3 HQDA Mode

In this mode the analogue input and digital output sections are disabled.

The DAC is synchronised to an external input (AES11 or digital audio input) as selected by the SYNC function.

Sync: Selects either AES11 or =IN (AES3) clock source.

indicates SYNC mode. Format Selects input format and interface

connectors.

Rate:

Incoming

Sync LED

Select: Configures output sample rate. mode. Monitor:

Selects either Mute or listen (Post) for both channels.

Level Up /Down controls.

Indicates the analogue output signal level.

#### 3.4 Convert Mode

In this mode the ADC is disabled and the LSC24 acts as a SRC with the DAC section used for monitoring.

This conversion is via the SRC unless '=in' SYNC mode is selected

Word:

Selects required output word length. 16,20 or 24 bit. 18 bit is not valid.

Format:

Selects output format and interface connectors.

Rate:

Selects required output sample rate or external sync.

Sync: Only valid if Rate set to Sync.

Selects either AES11 CLOCK =IN (AES3) clock source. Rate: Incoming sample rate.

Format: Selects input format and interface connectors. **Select**: Configures output mode.

Monitor: Selects either Mute or listen (Pre) for both channels. Level

Up /Down

controls.

Indicates the analogue output signal level.

# 4. Technical Description

## 4.1 Specification

## **Analogue-Digital Section**

Resolution 24 bits

Sample rates supported Internal 32kHz, 44.1kHz, 48kHz, 88.2kHz,

96kHz

External DARS (32kHz - 96kHz), Digital Audio

Input, 256Fs clock

Word Length 24, 20, 18 & 16bits

Sample rate frequency accuracy 50ppm

Noise and distortion At +18dBu≡0dB FS coding level,

Noise, RMS unweighted, 22-22kHz bandwidth

Noise: < -108dB FS

THD+N: < -102dB FS at -1dB below peak

coding

Max. Analogue Input Level +26dBu (with limiter off)

**Digital-Analogue Section**

Resolution 24 bits

Sample rates supported Internal 32kHz, 44.1kHz, 48kHz, 88.2kHz,

96kHz

External DARS (32kHz - 96kHz), Digital Audio

Input, 256Fs clock

Noise and distortion At +18dBu≡0dB FS coding level,

Noise, RMS unweighted, 22-22kHz bandwidth

Noise: < -110dB FS THD+N: < -100dB FS

Max. Analogue Output Level +26dBu

4.2 Dimensions

Width:- 483 mm (19" rack mount)

Height:- 44mm (1 <sup>3</sup>/<sub>4</sub>"- 1U) Depth:- 335 mm (max)

Weight:- 3Kg

# 5. Declaration of Conformity

# **DECLARATION OF CONFORMITY**

Manufacturers name Lindos Electronics

address Saddlemakers Lane Melton, Woodbridge

Suffolk IP12 1PP U.K.

Telephone +44 (0) 1394 380307 Fax +44 (0) 1394 385156 email info@lindos.co.uk

Product name Lindos Studio Converter - LSC24

Part number LSC2-RGUE-

Complies with the requirements of the European Low Voltage Directive and Electromagnetic Compatibility Regulations

and

conforms to the following standards:-

Safety: BS EN 61010-1:1993 and AMD 8691

**EMC:** BS EN 50081-1: 1992 (Emissions)

**BS EN 50082-1: 1998 (Immunity)**

**BS EN 60555-2: 1987 (Mains harmonics)**

Richard J Lincoln Date: 16 Oct 2000

**Development Manager**

Patricia M. Skirrow

**Proprietor**

Date: 16 Oct 2000